# Advancing High Voltage Power Module Packaging: Strategies for Partial Discharge Mitigation

Dr. Xiaoqing Song, Assistant Professor July 16, 2025

2025 Power Electronics & Energy Conversion Workshop

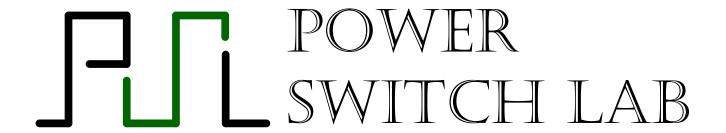

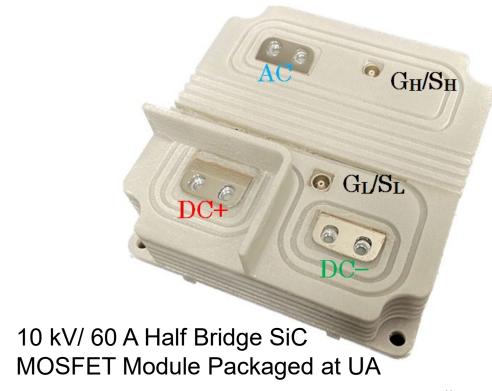

#### **High Voltage Power Devices — Status**

- Si: Current up to ~kA, but voltage limited to ~10kV

- SiC: Voltage up to ~20kV, but current limited to ~ 10s A

# RL

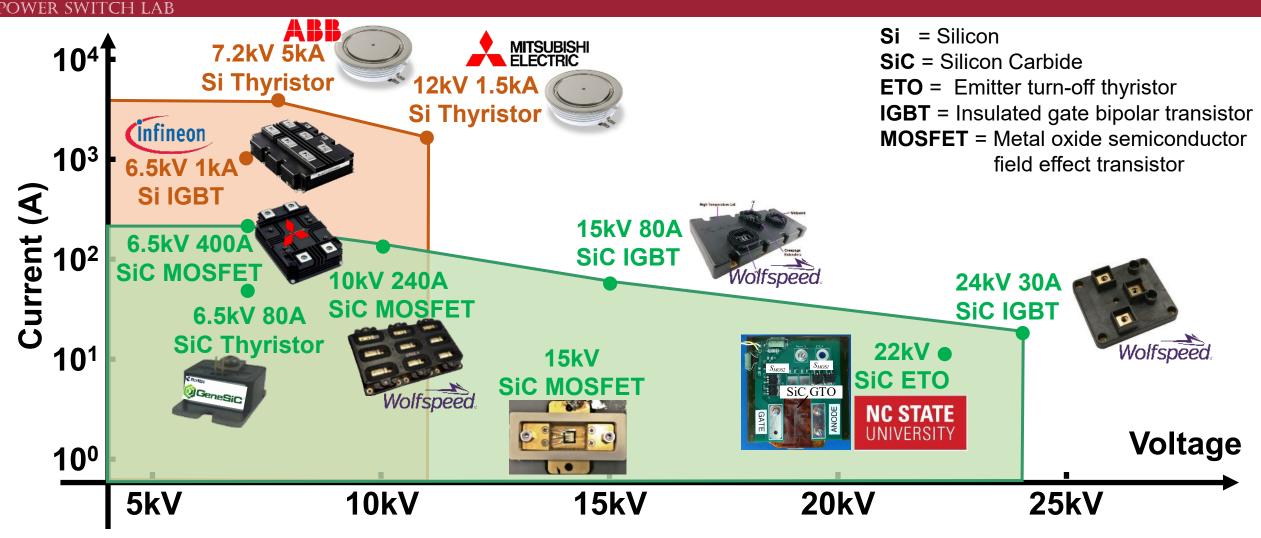

## **High Voltage Power Devices — Applications**

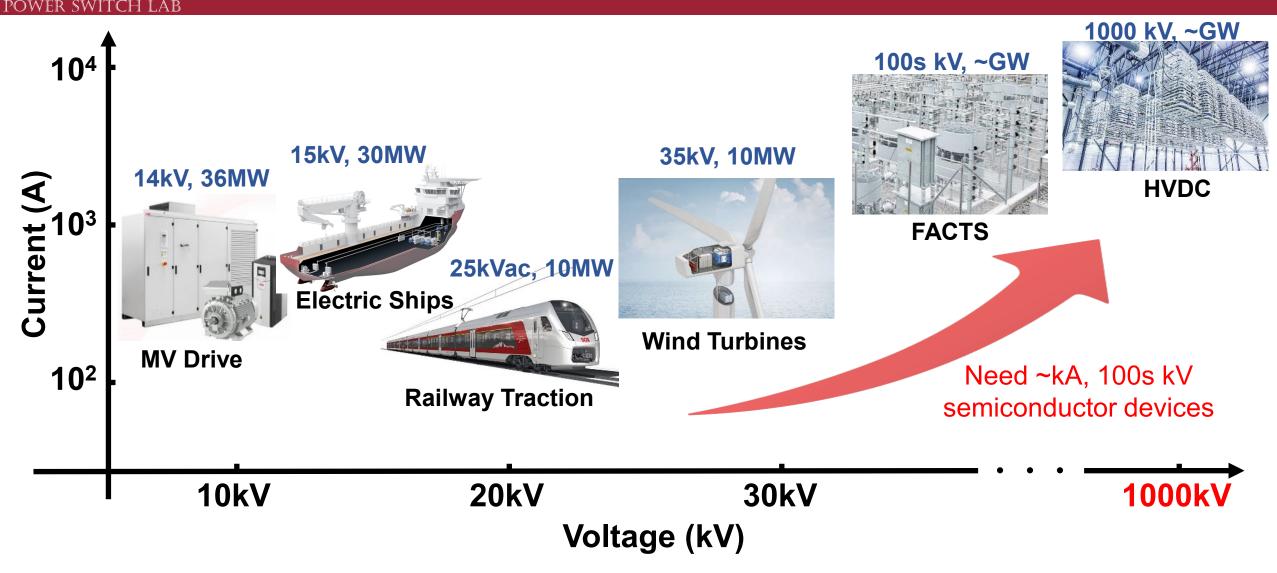

## **Benefits of HV Devices: An HVDC Example**

#### **High Voltage WBG Power Devices — Limitations**

#### **❖ Limited Voltage and Current Ratings**

- Voltage ratings remain low (< 30kV)</li>

- Current capability restricted to ~10s Amperes

#### Low Commercial Availability

- High cost

- No commercially available devices >10 kV

#### Reliability Concerns

- Unstable epitaxial growth

- Thermal management issues

#### ❖ High Voltage Module Packaging Challenges

- Voltage insulation Partial discharge

- Electromagnetic interference (EMI)

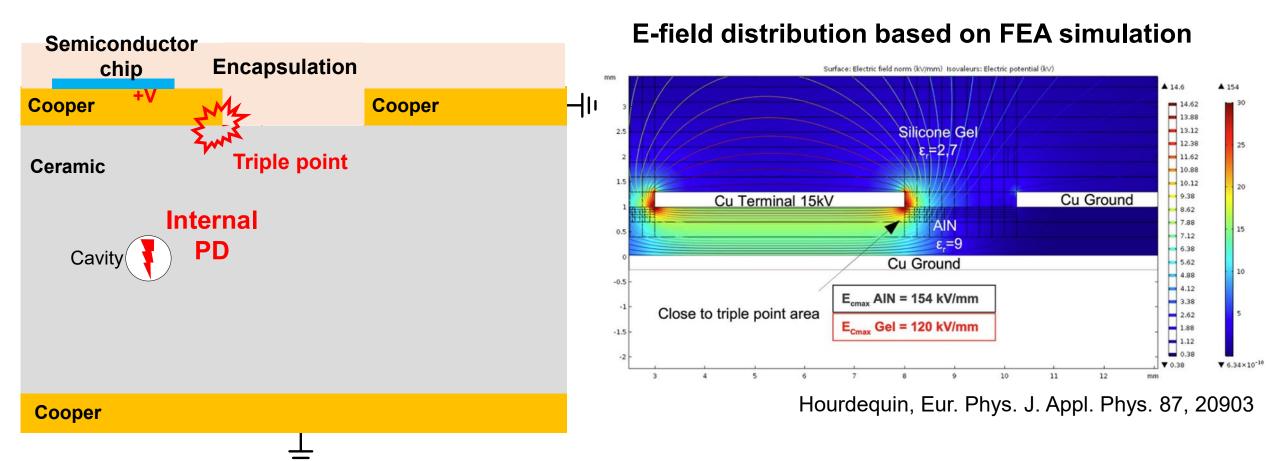

## Partial Discharge in HV Power Module Packaging

- Partial Discharge (PD) is self-sustaining electron avalanches that occur in regions of local high electric field strength

- ❖ PD → accelerated dielectric material aging → device failure

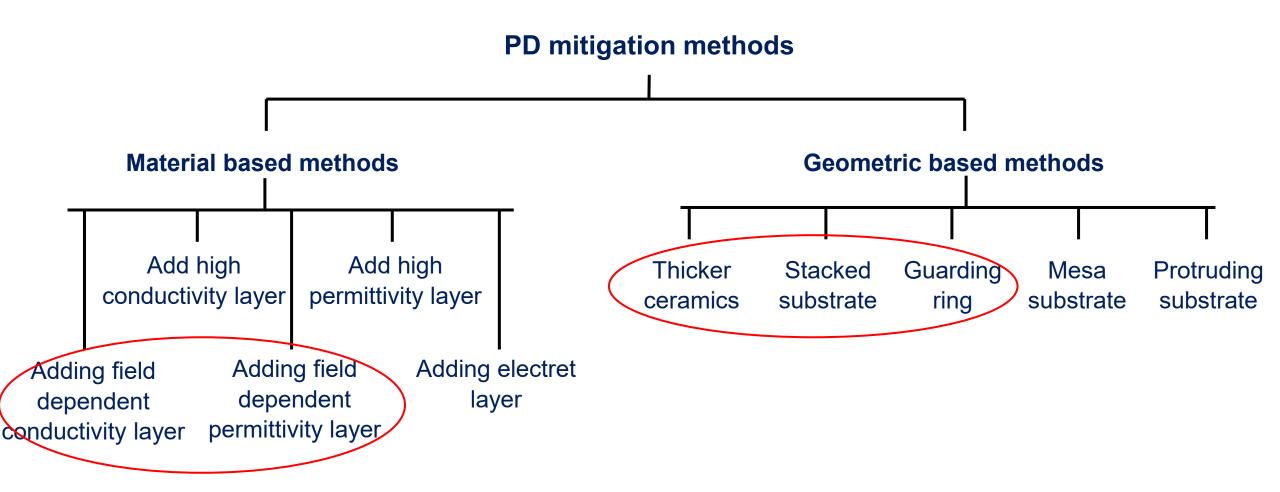

## PD Mitigation Techniques In Power Module Packaging

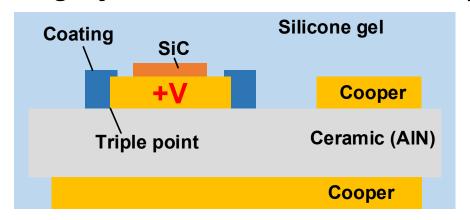

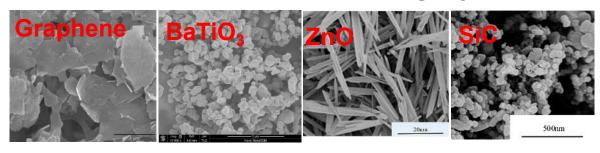

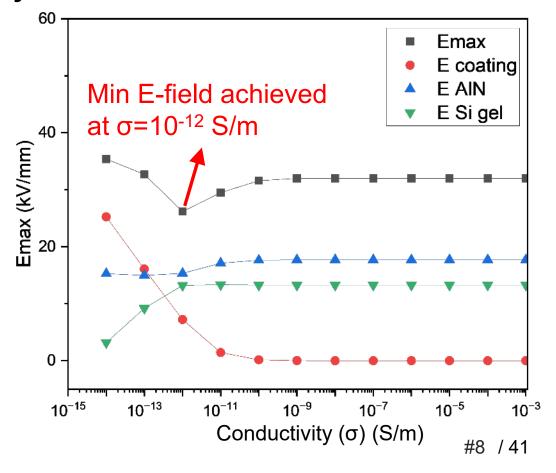

# Material Base Method – Modify Encapsulation Conductivity/ Permittivity

- **❖** Modify encapsulation conductivity and/or permittivity

- → Reduced E-field

- Coating layer with modified conductivity or permittivity

Nano particles added to the coating layer

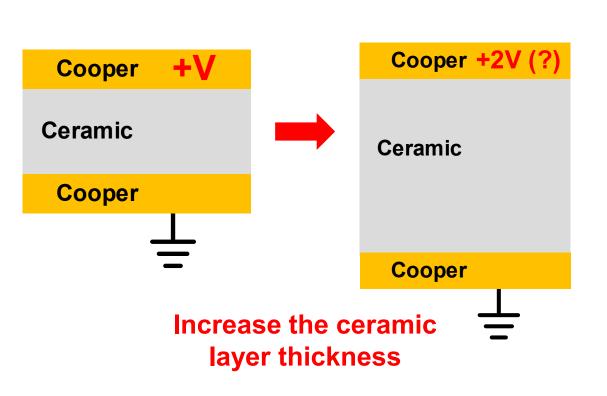

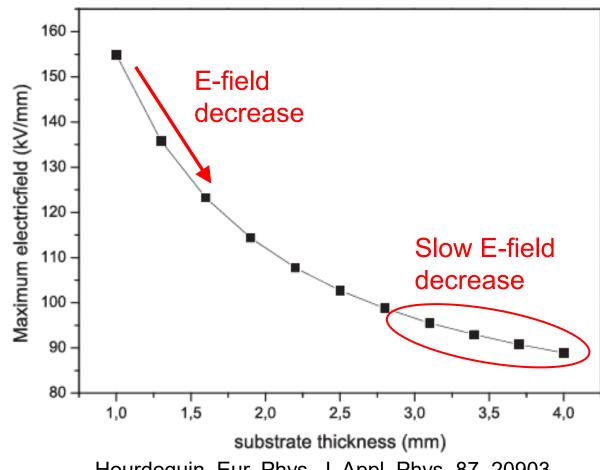

#### Geometric Design Method #1 – Thicker Substrate

- Hourdequin, Eur. Phys. J. Appl. Phys. 87, 20903

- Increasing ceramic layer thickness → Reduced E-field

- E-field trends to stable with thick enough ceramic layer

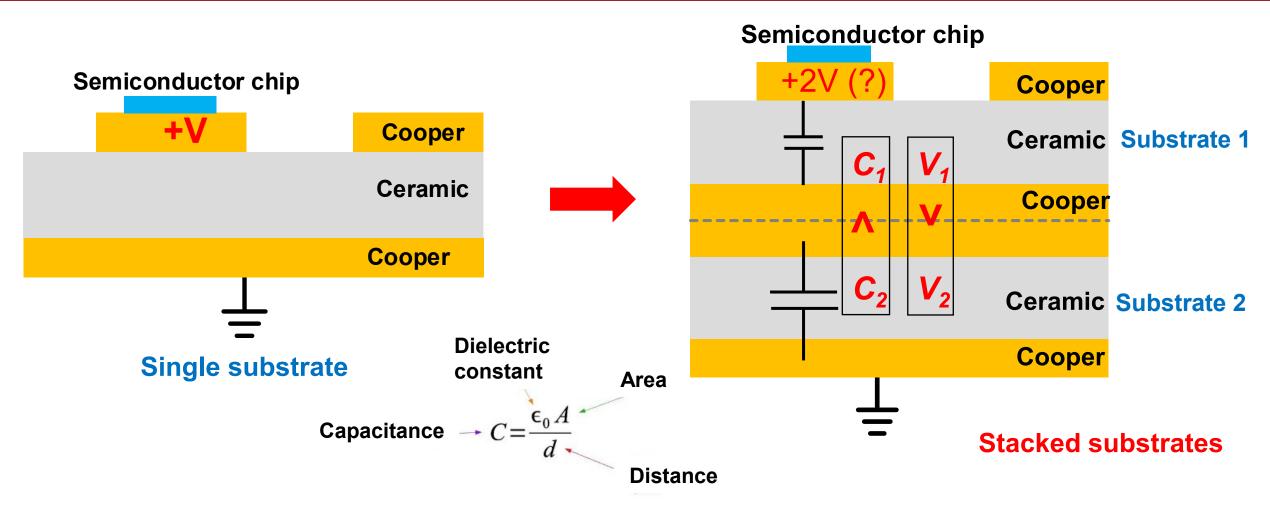

## Geometric Design Method #2 – Stacked Substrate

Directly stacking of substrates fails to reduce electric field due to unbalanced voltage sharing.

# Geometric Design Method #3 – Patterned Mid-layer Stacked Substrate

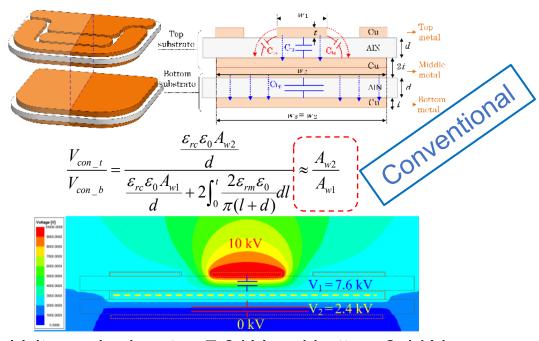

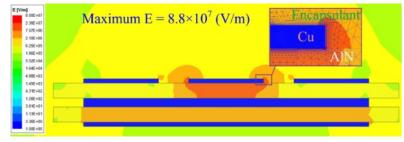

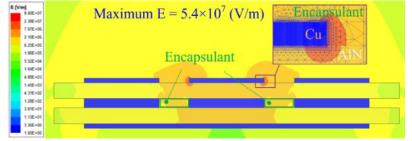

#### Solid Middle-layer Stacked Substrates

Voltage sharing: top 7.6 kV and bottom 2.4 kV

E-field distribution

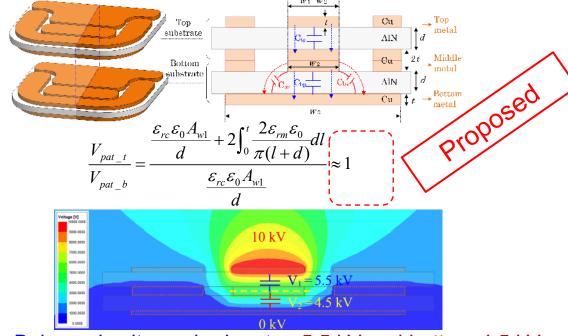

#### ❖ Patterned Middle-layer Stacked Substrates

Balanced voltage sharing: top 5.5 kV and bottom 4.5 kV.

Electric field distribution E-field reduction 38.6%

# **Summary and Future Work**

- Material based PD mitigation methods

- Easy to apply

- Effective in E-field reduction

- Geometric PD mitigation methods

- More complicated to fabricate

- Achieves more effective E-field reduction

- Future research topics

- More advanced PD mitigation methods

- PD modeling in encapsulation materials

- PD online detection and lifetime prediction

- **-** ...

# Thank you!